Cairo University

Faculty of Engineering

Department of Electronics

and Communications Engineering

Giza Campus

Midterm Exam - 23/11/2023

Electronics II - ELC2020

Fall Semester

| NA: | 140000 | Exam   |

|-----|--------|--------|

| IVI | atern  | ı exam |

(25 points)

Name: .....

B.N.: ......

Section: .....

"I have neither given nor received unauthorized aid on this examination, nor have I concealed any violations of the Honor Code."

Signature: .....

Unless otherwise stated, in the following problems, use the device data shown in the following table and assume that VDD = 3V where necessary. All device dimensions are in microns.

1

| Parameter         | NMOS<br>0.7 | PMOS<br>0.8 | Units V     |

|-------------------|-------------|-------------|-------------|

| $ V_{th} $        |             |             |             |

| λ                 | 0.1         | 0.2         | $V^{-1}$    |

| $K' = \mu C_{ox}$ | 139         | 38          | $\mu A/V^2$ |

Question #1: (5 points)

Chose the correct answer for each of the following questions:

- 1. To reduce the channel length modulation effect ( $\lambda$ ) of a MOS transistor,

- a) Reduce L

b) Reduce W

each point

c) Increase L

- d) Increase W

- 2. For a MOSFET in SAT region, to keep the drain current constant while increasing the transistor's aspect ratio (W/L),

- a) Increase  $V_{GS}$

b) Reduce Vov

c) Reduce  $V_{GS}$

- d) b and c

- 3. For a PMOS transistor in SAT region, the drain current is proportional to

- a)  $V_{GS} V_{THp}$

b)  $V_{SG} - V_{THp}$

c)  $V_{SG} + V_{THP}$

- d)  $V_{SG} + |V_{THP}|$

- 4. For a PMOS as an ON switch, the lowest  $R_{on}$  is achieved when the gate is connected to

- a) GND

b) VDD/2

c) VDD

d) It depends

- 5. Which  $V_A$  corresponds to higher  $r_o$ ?

- a) -50V

b) +50V

c) -100V

- d) + 100V

- 6. For two identical transistors having a size of (W/L) and are connected in series, the effective size of the combined two transistors is:

- a) W/L

W /21

c) 2W/L

- d) 2W /21

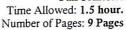

- 7. For the circuit shown below, the FULL range of  $V_D$  that will simultaneously bias the NMOS and PMOS in the saturation region is:

Page 1/9

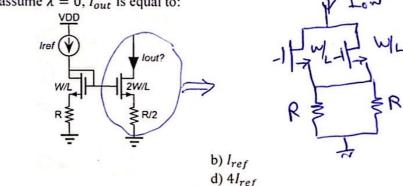

8. For the circuit shown below, assume  $\lambda = 0$ ,  $I_{out}$  is equal to:

a) 0.5*l*<sub>ref</sub> c) 2*l*<sub>ref</sub>

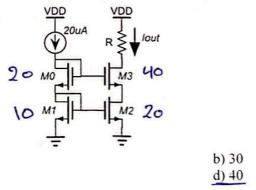

a) 10c) 20

9. For the cascode current mirror shown below, assume all transistors are operating in saturation. If  $(W/L)_0 = (W/L)_2 = 20$  and  $(W/L)_1 = 10$ . What should  $(W/L)_3$  be for a proper operation?

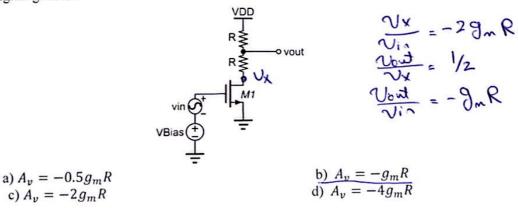

10. For the common source amplifier shown below, assume M1 is in saturation and  $\lambda = 0$ . The small signal gain is:

Page 2/9

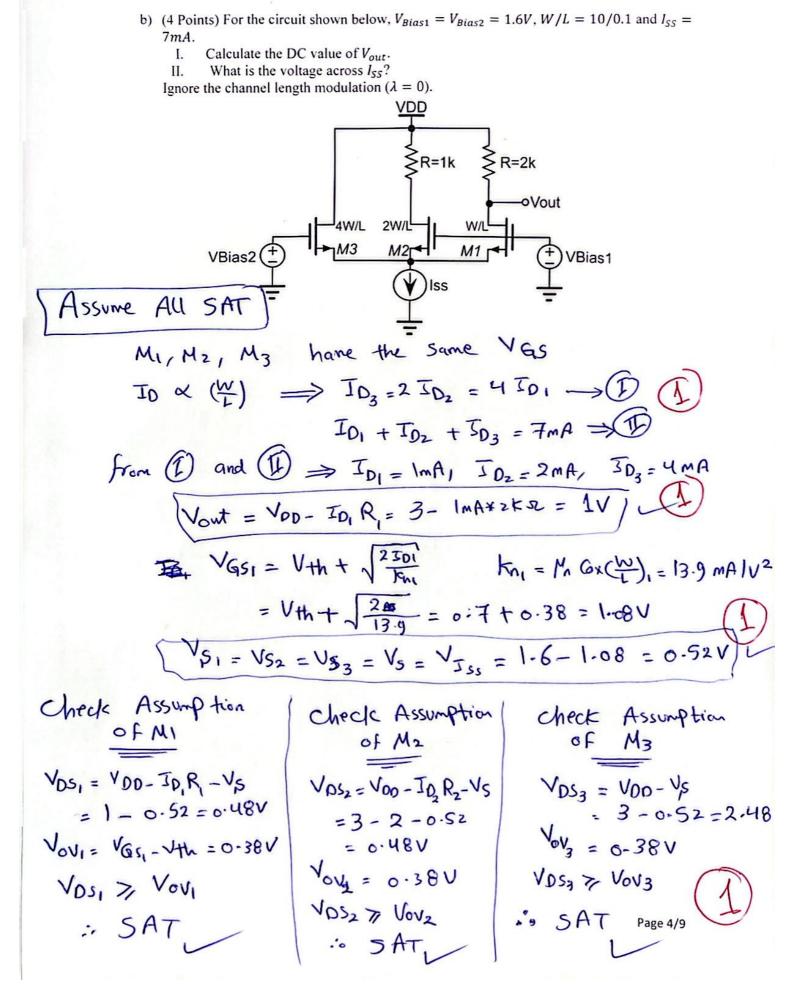

Question #2: (6 points)

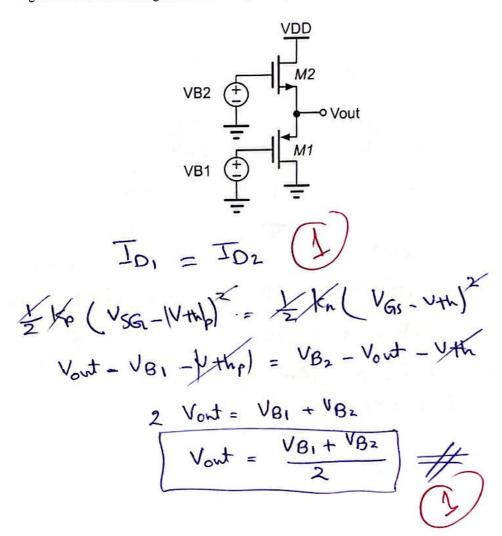

a) (2 Points) For the circuit shown below, derive an expression for the DC value of the  $V_{out}$  as a function of bias voltages  $V_{B1}$  and  $V_{B2}$ . Assume both transistors are in SAT,  $K_p = K_n$  and  $V_{THN} = |V_{THP}|.$

Ignore the channel length modulation ( $\lambda = 0$ ).

## Scanned with CamScanner

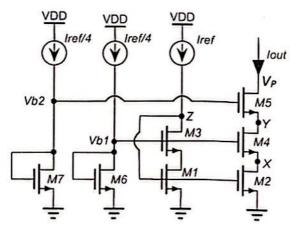

## Question #3: (7 points)

For the current mirror circuit shown below,  $I_{ref} = 100\mu A$ . M4 and M5 double cascode the current source M2. Transistors M1 – M5 are identical having size of W/L = 10/0.1.

Both M6 and M7 are used to bias cascode devices.

Assume all transistors are in saturation. Consider channel length modulation.

- a) What is Iout?

- b) What is the minimum value of  $V_p$  that ensures M2, M4 and M5 are in SAT?

- c) What is the optimal value of  $V_p$  that ensures there is no current mismatch between  $I_{out}$  and  $I_{ref}$ ?

- d) What is the optimal bias voltage  $V_{b1}$  for M3/M4?

- e) What is the optimal bias voltage  $V_{b2}$  for M5?

- f) What is the size of M7  $(W/L)_7$  required to generate the bias voltage  $V_{b2}$  obtained in (e)? Ignore  $\lambda$  in your calculations. Assume  $V_{th} = 0.3V$ .

$$\sqrt{\frac{0.1}{2 \times 0.139 + (\frac{10}{L})_{T}}} = 0.3 + \sqrt{\frac{0.2}{13.9}}$$

$$\frac{\left(\frac{V}{L}\right)_{7}}{1} = 1.234 = \frac{0.1234}{0.1}$$

Page 6/9

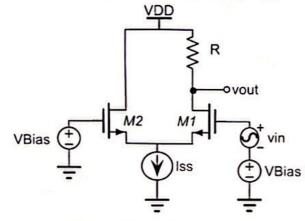

## Question #4: (7 points)

For the amplifier shown below, assume M1 and M2 are identical and in saturation.

- a) What is the DC current in M1 and M2? (Ignore  $\lambda$  here only).

- b) What is the DC voltage of  $V_{out}$ ?

- c) What is the configuration of this amplifier?

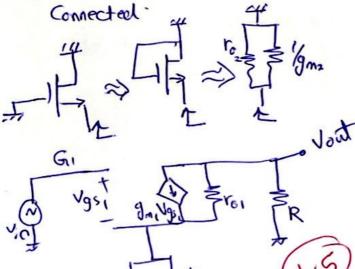

- d) Draw the small signal model.

- e) Derive an expression for the amplifier transconductance  $(G_m)$

- f) Derive an expression for the amplifier output impedance  $(R_{out})$

- g) Derive an expression for the small signal gain  $(A_v = v_{out}/v_{in})$

a)

$$T_{0_1} = T_{0_2} = \frac{T_{SS}}{2}$$

$\Longrightarrow \lim_{L \to \infty} \lim_{L \to \infty} \frac{1}{2} \lim_{L \to \infty} \frac{1}$

d) M2 in small signal is diade

## Scanned with CamScanner